シーケンス学習向けに手軽に実動作確認ができる「簡易シーケンス検定盤」を紹介しましたが、これを使って標準ロジックIC 4個の超低性能1bitCPUをベースに、外部入力機能を追加して簡単なコンベア往復のみのシーケンス制御をさせてみました。今回利用しませんでしたがこの1bitCPU基板キットも市販されています。

オリジナルの超低性能CPUは、1bitの加算と、アドレス1bitのジャンプの2つの命令のみでしたが、外部から制御をさせるために外部入力命令を追加するついでに、下記の4つの命令に回路変更してみました。

00 INC A (Aレジスタに1加算)

01 ADD IN,A (Aレジスタに1bit外部入力値を加算)

10 LD IN,A (Aレジスタに1bit外部入力値を代入)

11 JMP IN (1bit外部入力値のアドレスにジャンプ)

変更した超低性能1bitCPU改 回路図

今回のシーケンス制御は

ADD IN,A (Aレジスタに1bit外部入力値を加算)

の無限ループで処理を実現しています。

動作としては左右のリミットスイッチのONを負論理としてIN端子から検出し、スイッチONとなった時にAレジスタに1加算することで、Aの値が反転し、コンベアが反転して往復します、ただそれだけ。1bit入力のみのためリミットスイッチは、左右共通にしていますが、CPUの動作周波数が1Hzと遅いためこれでも問題なく動作します。

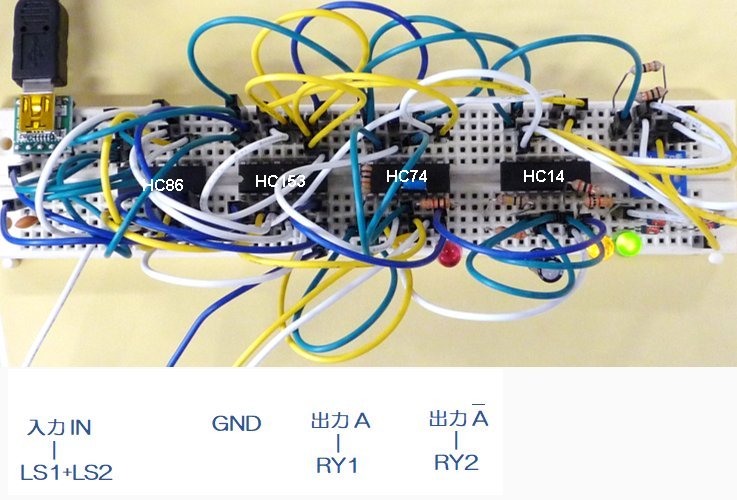

ごちゃごちゃしていますが実際にブレッドボードに組んで、簡易シーケンス検定盤につなげて動作確認した1bitCPU改回路です。これでコンベアがちゃんと往復しています。これと同じ動作を論理回路で実現するだけならもっとシンプルな回路で実現できますが、シーケンサとして1bitCPUで動作させたところがミソです。

超低性能1bitCPU改 試作回路

ちなみに、高性能な1bitプロセッサとしては、モトローラ社のMC14500というICがありました。

これもシーケンス制御用に開発されたそうです。

こんな記事が見つかりました。参考まで。

http://www.st.rim.or.jp/~nkomatsu/motorola/MC14500.html

https://www.techno-edge.net/article/2024/03/11/2950.html

https://ja.wikipedia.org/wiki/MC14500B